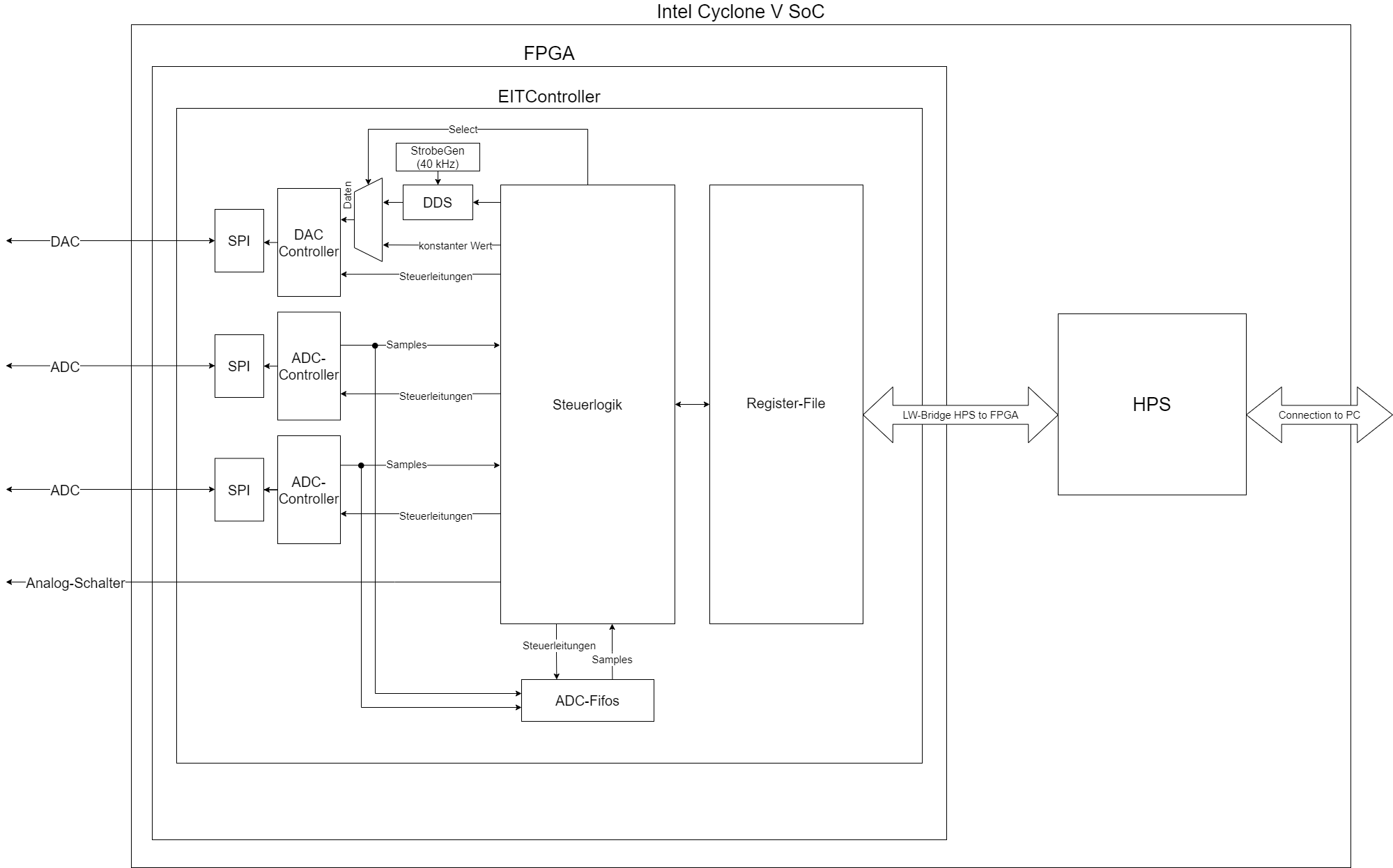

FPGA

Register-File

Die Controller des FPGAs werden vom HPS im Treiber mit dem Register-File konfiguriert. Mögliche Parameter inkludieren Frequenz und Amplitude des Sinus, das Elektrodenpaar mit dem gemessen wird, Einspeisende Elektrode, etc.

Direct Digital Synthesis

Erzeugt sinosoidale Signale bis zu 40kHz die über die Elektroden eingespeist werden.

ADC-FIFOs

Es werden zwei FIFOs verwendet. Eine für die Spannung nach dem Shunt-Widerstand, eine für die Spannung zwischen den Messelektroden.

Steuerlogik

Übernimmt unter anderem die Steuerung des Messablaufs um korrekte Messwerte zu erhalten